Release laysim-NOELV v0.1

laysim-NOELV v0.1 Quad Core Processor Emulator

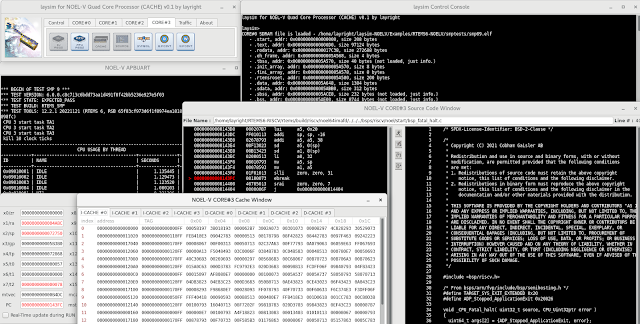

I'm really proud to release laysim-NOELV v0.1 based NOEL-XCKU-20210208 (GP64L-QC. 100MHz).

laysim-NOELV consists of three types of emulators: laysim-noelv, laysim-noelv-dbt and laysim-noelv-mdbt. They are provided as a stand-alone application as well as a set of libraries that can be integrated in an existing simulator.

laysim-noelv is a graphic user interface (GUI)-based and cycle-accurate emulator for the NOEL-V quad core processor from NOEL-XCKU-20210208 (GP64L-QC) based on interpretation method. It includes an embedded source-level debugger and L1/L2 caches.

laysim-noelv-dbt is a GUI-based high-performance and cycle-approximate processor emulator with dynamic binary translation method.

laysim-noelv-mdbt (Multi-Thread DBT, only CLI version) is a parallel implementation of laysim-noelv-dbt, where it adopts the multi-thread framework with DBT so it can exceed the real-time performance of NOEL-V on a high-end PC such as Intel i9-12900K.

1. laysim-NOELV Overview

laysim-NOELV emulates the NOEL-V quad core processor according to NOEL-XCKU-20210208 (GP64L-QC).

- NOEL-V quad core processor (0x01:0x0BD) with 100MHz clock

- NOEL RISC-V RV64IMAFD with NanoFPU (Currently C, S, H extensions are not supported)

- 16KB 4-way instruction cache and 16KB 4-way data cache and 256KB Level-2 cache only for laysim-noelv

- RISC-V CLINT (0x01:0x0C3) and RISC-V PLIC (0x01:0x0C2) are supported

- MMU(Memory Management Unit) and PMP (Physical Memory Protection) are not supported yet

- Supported GRLIB devices of NOEL-XCKU : GRGPIO (0x01:0x01A), GPTIMER (0x01:0x011), APBUART (0x01:0x00C)

- Unsupported GRLIB devices of NOEL-XCKU : AHBSTAT (0x01:0x052) - need to more test

- Memory : 8MB AHBROM and 128MB SDRAM

2. Quick Comparison laysim-NOELV

Core | laysim-noelv | laysim-noelv-dbt | laysim-noelv-mdbt |

Emulator Type | Interpreter - For S/W development and debugging | DBT (Dynamic Binary Translation) - Aim for fast execution and simulation | Multi-Thread DBT (Parallel) - To meet the real-time performance of NOEL-V under the SMP environment - Require at least 4 x64 cores |

Cycle Accuracy | Cycle accurate Max ±5% error rate | Cycle approximate Max ±10% error rate | Cycle approximate Max ±10% error rate |

L1/L2 Cache | Fully implemented | No L1/L2 cache for speed-up | No L1/L2 cache for speed-up |

Multicore Emulation | Instruction & Cycle level - Execute a instruction from the lowest local cycles of core every time | Round-robin fashion on time quantum (Default time quantum is 1000) - 1 means 10nsec on 100MHz, so 1000 is 10usec | Parallel execution based on time quantum (Default is 1000) - 1 means 10nsec on 100MHz, so 1000 is 10usec |

The time quantum can be changed using '-quantum' start-up option | |||

Control Console | Support - Can control emulation and check status of cores and memory - Can check the performance and information | Support - Can control emulation and check status of cores and memory - Can check the performance and information | Support - Can control emulation and check status of cores and memory - Can check the performance and information |

GDB | Fully Supported - laysim-noelv includes the embedded source-level debugger, so it is possible to debug NOEL-V application without GDB. | Fully Supported | Fully Supported |

Real-Time Performance (RTP)

i9-12900K @5Gz | 1) Single Core - 47.72% RTP on NCC dhrystone - 473.24% RTP on NCC whetstone SP

2) Multi Core - 14.63% RTP on NCC dhrystone - 21.10% RTP on NCC whetstone SP - 15.71% RTP on smpmigration02 - 14.40% RTP on smpmrsp01 | 1) Single Core - 1438.55% RTP on NCC dhrystone - 2380.92% RTP on NCC whetstone SP

2) Multi Core - 209.65% RTP on NCC dhrystone - 179.90% RTP on NCC whetstone SP - 261.71% RTP on smpmigration02 - 169.50% RTP on smpmrsp01 | 1) Single Core - 948.75% RTP on NCC dhrystone - 1226.42% RTP on NCC whetstone SP

2) Multi Core - 640.16% RTP on NCC dhrystone - 473.03% RTP on NCC whetstone SP - 619.27% RTP on smpmigration02 - 568.19% RTP on smpmrsp01 |

3. Performance of laysim-NOELV

laysim-noelv-dbt and laysim-noelv-mdbt can exceed the real-time performance (RTP) of NOEL-XCKU-20210208 (GP64L-QC, 100MHz)

| laysim-noelv | laysim-noelv-dbt | laysim-noelv-mdbt | |||

| Raw MIPS | RTP | Raw MIPS | RTP | Raw MIPS | RTP |

Dhrystone (single) | 49.41 | 47.72% | 1489.93 | 1438.55% | 982.64 | 948.75% |

Dhrystone (Multi) | 59.02 | 14.63% | 846.10 | 209.65% | 2583.51 | 640.16% |

Whetstone (single) | 39.59 | 473.24% | 208.64 | 2380.92% | 107.47 | 1226.42% |

Whetstone (Multi) | 65.06 | 25.10% | 825.33 | 179.90% | 2170.07 | 473.03% |

RTEMS6 smpmigration02 | 18.16 | 15.71% | 515.72 | 261.71% | 1127.12 | 619.27% |

RTEMS6 smpmrsp01 | 32.89 | 14.40% | 454.50 | 169.50% | 1473.50 | 568.19% |

RTEMS6 smpmulticast01 | 31.36 | 14.54% | 664.06 | 249.92% | 1315.51 | 501.84% |

RTEMS6 smpmutex02 | 28.16 | 15.27% | 320.45 | 126.38% | 1421.30 | 576.52% |

RTEMS6 smpschededf03 | 33.39 | 13.40% | 519.58 | 176.71% | 1495.13 | 494.34% |

4. Limitation of laysim-NOELV Evaluation Version

5. Download laysim-NOELV Evaluation Version

The evaluation version of laysim-NOELV and user's manual can be downloaded from Download Article (https://layright.blogspot.com/2020/02/download-laysim-leon3.html).

댓글

댓글 쓰기